482

Інженери розробили експериментальний 36-ядерний процесор

Науково-дослідницькі роботи Інституту технології Массачусетса (МІТ) не оголошують експериментальний 36-ядерний процесор. Новинка, згідно з розробниками, здатна підвищити продуктивність чіпів сучасної архітектури до нового рівня.

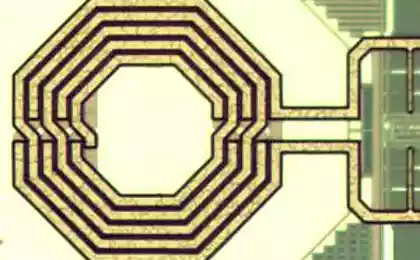

За словами творців нового продукту, чіп призначений для зменшення кількості циклів, необхідних для виконання складних завдань. Процесор має складну логіку передачі даних між ядерами та інтелектуальною системою пам'яті кешу. Розробники чіпа Інституту комп'ютерних наук МІТ говорять, що чіп інтегрував мережу міні-роутерів, які допомагають сортувати та керувати даними.

Міні маршрутизатори є одним з родзинок 36-ядерного чіпа. Вони є інтелектуальним способом маршрутизації даних в процесорі, так що пропускна здатність автобуса використовується максимально ефективно, і ядра процесора навантажуються пропорційно. Розробники кажуть, що реальний потенціал чіпа буде розблоковано, коли він працює з багаточитаними додатками, такими як фінансові аналітичні продукти або програмне забезпечення для імітації фізичних процесів.

Чіпс розвивається теоретична модель «шадової мережі», в якій пам'ять кешу дозволяє зберегти дані з деяких процесорних ядер і не рятувати з інших. Крім того, модель дозволяє збити великі пакети інформації на невеликі та розподілити їх обробку через ядра, в той час як самі ядра можуть спілкуватися один з одним для узгодження процесів обробки даних.

У майбутньому експерти мають намір створити 64-ядерний процесор на основі інтелектуальної моделі.

Джерело: Globalscience.ru

Технологія розпізнавання обличчя для діагностики генетичних захворювань

Сонячна фарба є джерелом відновлюваної енергії