478

工程师开发了一个实验36-核处理器

研究人员来自马萨诸塞技术学院(MIT)rasabali实验36-核处理器。 新颖性,根据开发,是能够提高性能的芯片的现代建筑一个新的水平。

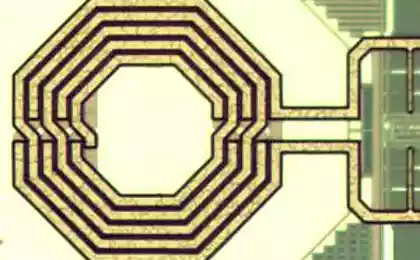

根据创作者的新的芯片设计减少所需的周期来执行复杂的任务。 处理具有复杂逻辑的数据之间传递的核心和智能系统的高速缓存。 开发商的芯片研究所的计算机科学在麻省理工学院告诉我们,在芯片上的综合网络的小型路由器,其排序和管理数据。

小路—这是一个突出的36-芯片。 他们表示一种智能的方式的路线数据的内部CPU使带宽的总使用尽可能有效地,和处理核装成比例。 开发者说,真正的潜力的芯片会发现时,它将与多线程应用程序,例如金融分析产品或软件来模拟物理过程。

芯片研发一个理论模型的一个"影子网络",其中高速缓冲存储器可以储存数据从一个处理核心,而不要让其他人。 该模型还可以打败大包的信息在小和分发他们处理跨越的核心,核可相互协调数据处理。

在未来,该专家打算创建一个64核处理器基于智能模式。

资料来源:globalscience.ru