1480

Intel reveló planes para conquistar 10 y 7 nm

Un mayor desarrollo de los microprocesadores puede requerir una

sin silicona

tema de la Conferencia Internacional sobre circuitos semiconductores ( Internacional Solid-State Circuits Conference ) en Este año, sonaba como un "pequeños chips para grandes volúmenes de datos." El evento se llevó a cabo del 22 al 26 de febrero en San Francisco, California, EE.UU.. Intel participa regularmente en ISSCC, no fue la excepción y 2015. Tamaño para los Gigantes de Intel y AMD no es inusual para hacer un anuncio importante allí. Muchos informes dijeron a las investigaciones internas de Intel, que se refirió a la posibilidad de una aplicación real de la tecnología, que incluye además la reducción de los chips de tecnología de procesos. En particular, tocado este apasionante tema de cómo atacar la Ley de 10 nanómetros de Moore.

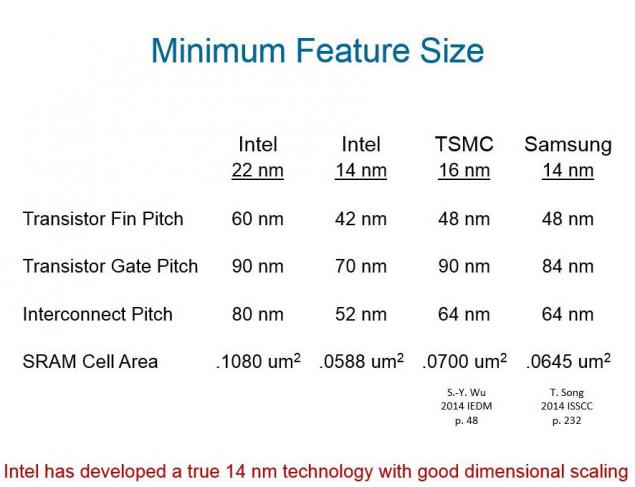

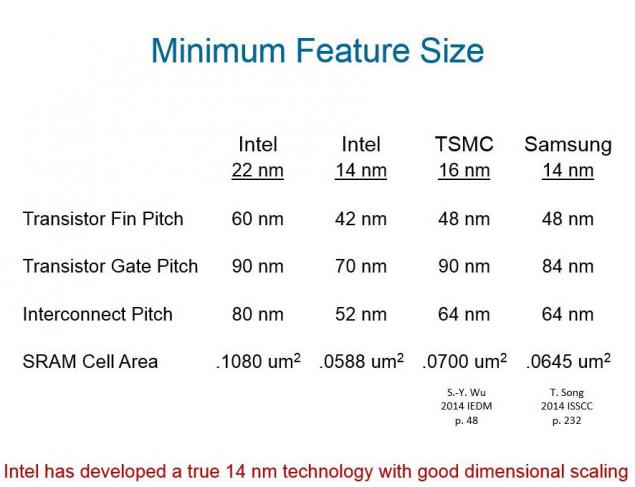

Intel está orgulloso de la conquista de 14 nanómetros. Este logro se dio con dificultad y demoras en 6-9 meses, dependiendo del tipo de producto, pero la compañía se las arregló para lograr un rendimiento superior de Samsung y TSMC. Intel cree que sólo se las arreglaron para conseguir este 14 nm:. Hablar de ello elementos más pequeños individuales, y otras características, como el tamaño de la celda SRAM

Intel predice que la transición a 10nm va a mejorar, pero el tiempo específico de las entregas no fue llamado. Si usted se centra en planes anteriores, el 10 nm será lanzado a finales de 2016 o principios de 2017. 10 nm y una mayor reducción se dará a muy dura. Intel aprende de sus errores en el trabajo de 14 nm y espera evitar el mismo error cuando se mueve a 10.

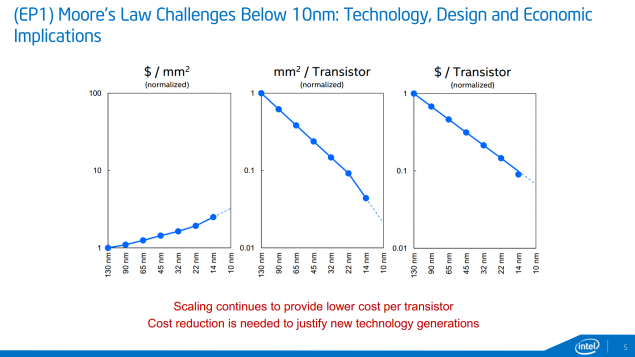

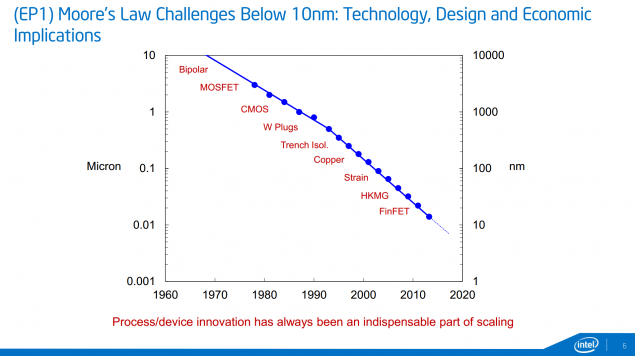

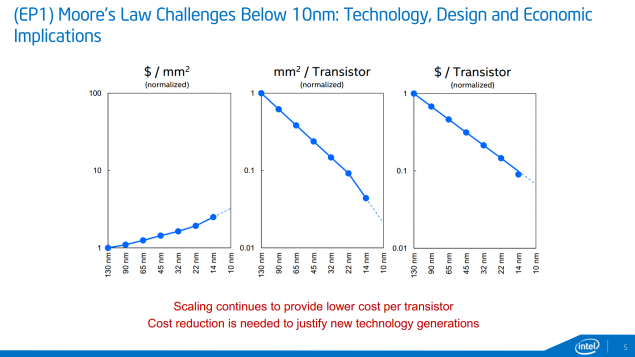

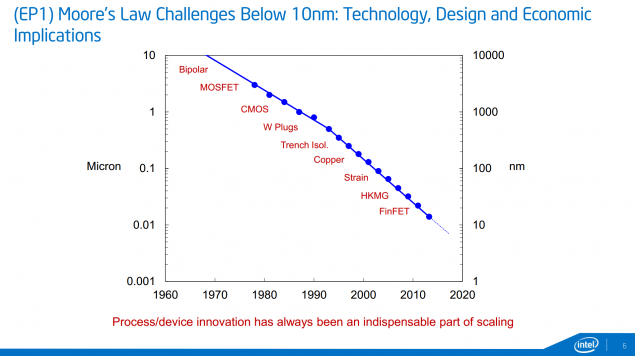

La pregunta era también sobre el coste del proceso. En la gráfica de la marca Bohr, se puede ver cómo el abaratamiento de los elementos individuales. Se puede observar que 14 nm mostraron una disminución ligeramente más grande en valor de lo esperado. Esto se logró mediante la optimización del proceso de litografía y el uso de máscaras. Y que 10 nm pasos el uso de máscaras será aún más retrasos que hemos visto en la situación de los 14 no lo hará. Intel ha dado cuenta de que las demoras fueron causadas por el 14 nm mayor número de pruebas e inspecciones. Como resultado, corrección de potencia PV prueba de funcionamiento 10 nanómetros y media veces más rápido que en el caso de 14 nm. Deje que los costos fijos serán superiores a 10 nanómetros, pero el costo caerá al transistor utilizando las mismas técnicas de litografía. Intel considera el глубокий UV, pero no quiere usarlo a menos que sea absolutamente necesario debido al proceso lento de su desarrollo de lo esperado.

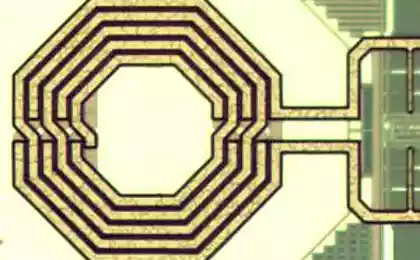

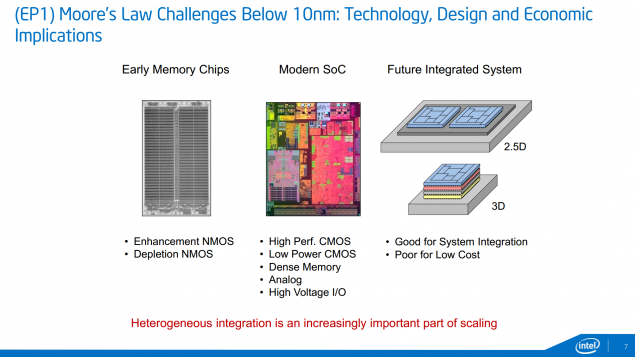

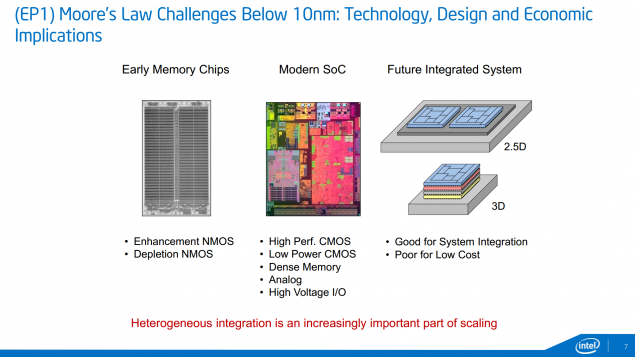

Además, el equipo de investigación habló sobre el uso de la tecnología Intel 3D (capa por capa) y 2.5D (capas individuales en el sustrato). Estas soluciones pueden darse el lujo de colocar más transistores: en algunos casos, limitar el consumo de energía (2.5D) o construir un diseño más compacto (3D). En particular, Intel está considerando escenarios en los que los circuitos lógicos de los diferentes métodos de producción se apilan en capas en lugar de la aplicación de una sola capa de este tipo. Esto puede aparecer en dispositivos móviles -. Smartphones, tabletas

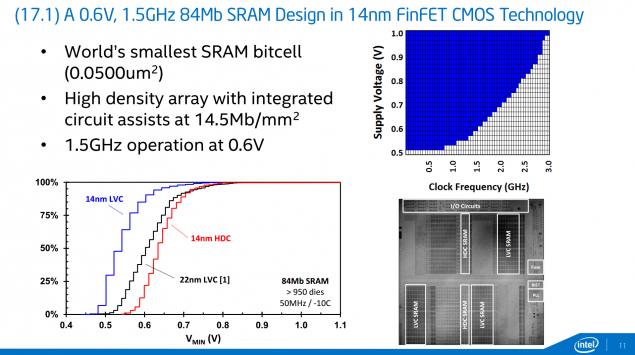

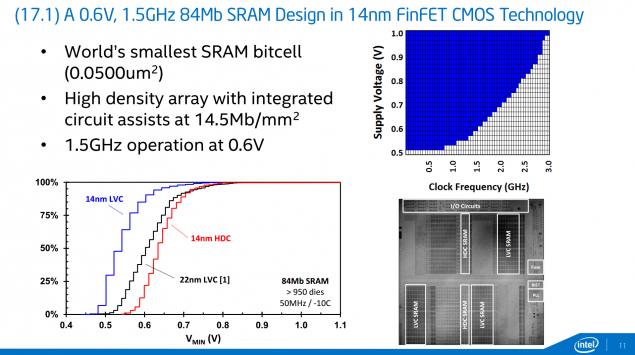

La novedad más interesante de la tecnología de 14 nanómetros puede ser SRAM: Intel llegó a un almacenamiento de 84 megabits con tamaño de celda más pequeño del mundo - 0, 050 mkm². Este 14 5 megabits por milímetro cuadrado. En comparación con 22 nm voltaje requerido caído 0, 1 a 6, 5 GHz, de 1 a 3 GHz.

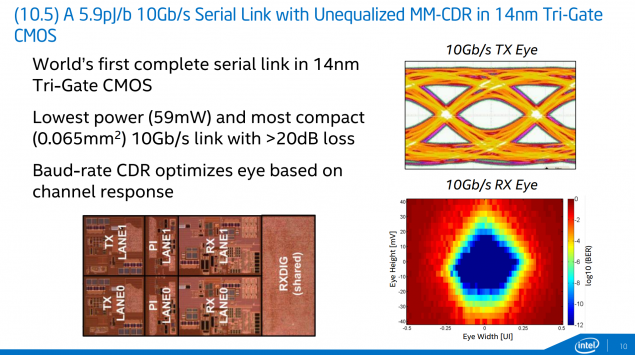

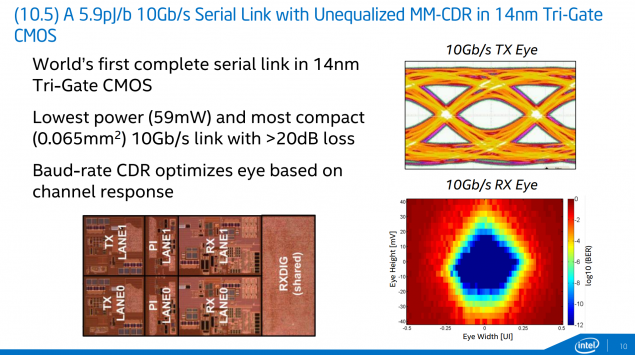

Intel logra un dato muy económico: 10 Gbit / s sólo 5 requiere, 9 pJ por bit em>

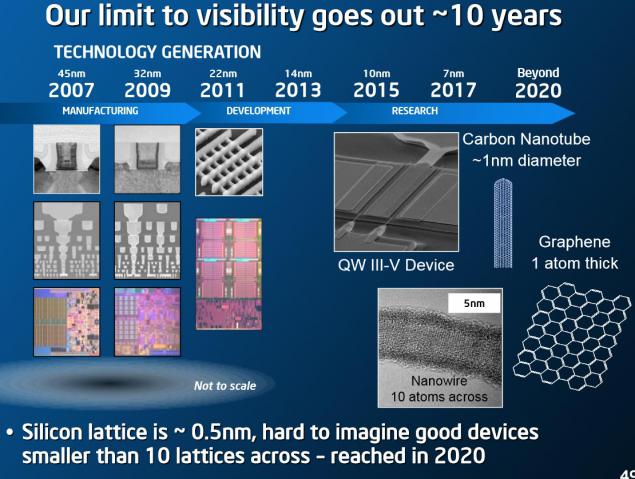

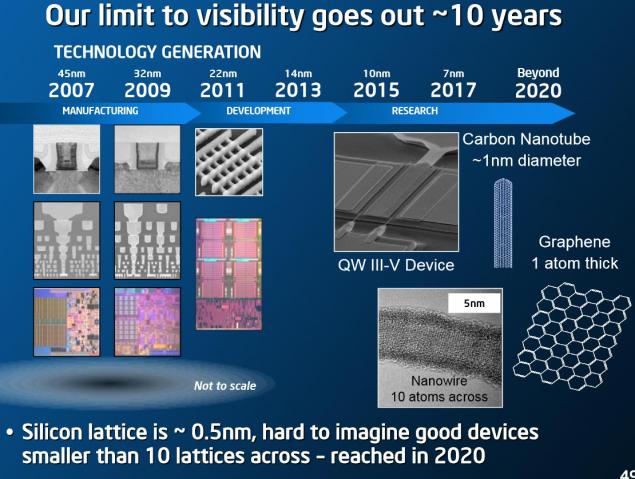

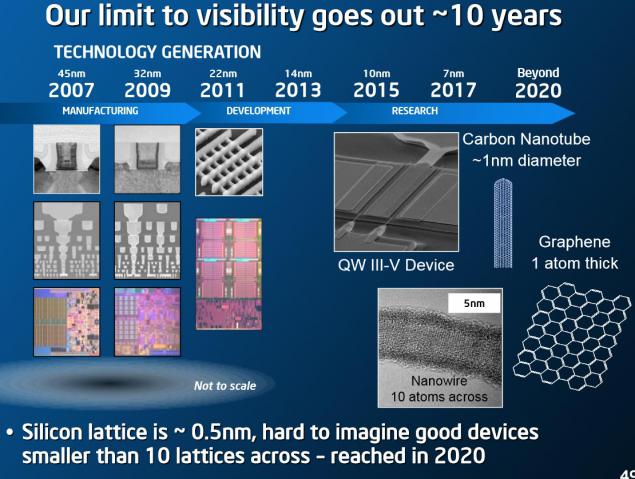

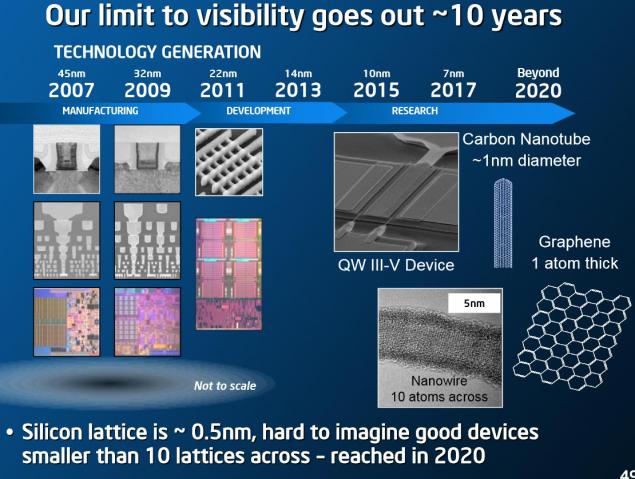

10 nanómetros se requieren innovación y la transición a siete en total sólo será posible con nuevos materiales y procesos. Pero nada concreto no ha sido nombrado, aunque discutido semiconductores III-V. Esta va combinaciones de elementos del tercer grupo de la tabla periódica (aluminio, galio, indio) de los elementos del grupo del quinto (nitrógeno, fósforo, arsénico, antimonio). La movilidad de los electrones en ellos es mayor que el de silicio, que permite reducir el tamaño de los transistores. En Intel начали ven de esta manera hace unos años, tal vez dentro de unos años será el núcleo del chip de computadora en el arseniuro de galio indio.

mayor progreso se ve muy futurista: posible ultravioleta profundo, los nanotubos de carbono, los nanocables de grafeno y em>

Basado en el material Ars Technica, ExtremeTech y AnandTech.

Fuente: geektimes.ru/post/246676/

sin silicona

tema de la Conferencia Internacional sobre circuitos semiconductores ( Internacional Solid-State Circuits Conference ) en Este año, sonaba como un "pequeños chips para grandes volúmenes de datos." El evento se llevó a cabo del 22 al 26 de febrero en San Francisco, California, EE.UU.. Intel participa regularmente en ISSCC, no fue la excepción y 2015. Tamaño para los Gigantes de Intel y AMD no es inusual para hacer un anuncio importante allí. Muchos informes dijeron a las investigaciones internas de Intel, que se refirió a la posibilidad de una aplicación real de la tecnología, que incluye además la reducción de los chips de tecnología de procesos. En particular, tocado este apasionante tema de cómo atacar la Ley de 10 nanómetros de Moore.

Intel está orgulloso de la conquista de 14 nanómetros. Este logro se dio con dificultad y demoras en 6-9 meses, dependiendo del tipo de producto, pero la compañía se las arregló para lograr un rendimiento superior de Samsung y TSMC. Intel cree que sólo se las arreglaron para conseguir este 14 nm:. Hablar de ello elementos más pequeños individuales, y otras características, como el tamaño de la celda SRAM

Intel predice que la transición a 10nm va a mejorar, pero el tiempo específico de las entregas no fue llamado. Si usted se centra en planes anteriores, el 10 nm será lanzado a finales de 2016 o principios de 2017. 10 nm y una mayor reducción se dará a muy dura. Intel aprende de sus errores en el trabajo de 14 nm y espera evitar el mismo error cuando se mueve a 10.

La pregunta era también sobre el coste del proceso. En la gráfica de la marca Bohr, se puede ver cómo el abaratamiento de los elementos individuales. Se puede observar que 14 nm mostraron una disminución ligeramente más grande en valor de lo esperado. Esto se logró mediante la optimización del proceso de litografía y el uso de máscaras. Y que 10 nm pasos el uso de máscaras será aún más retrasos que hemos visto en la situación de los 14 no lo hará. Intel ha dado cuenta de que las demoras fueron causadas por el 14 nm mayor número de pruebas e inspecciones. Como resultado, corrección de potencia PV prueba de funcionamiento 10 nanómetros y media veces más rápido que en el caso de 14 nm. Deje que los costos fijos serán superiores a 10 nanómetros, pero el costo caerá al transistor utilizando las mismas técnicas de litografía. Intel considera el глубокий UV, pero no quiere usarlo a menos que sea absolutamente necesario debido al proceso lento de su desarrollo de lo esperado.

Además, el equipo de investigación habló sobre el uso de la tecnología Intel 3D (capa por capa) y 2.5D (capas individuales en el sustrato). Estas soluciones pueden darse el lujo de colocar más transistores: en algunos casos, limitar el consumo de energía (2.5D) o construir un diseño más compacto (3D). En particular, Intel está considerando escenarios en los que los circuitos lógicos de los diferentes métodos de producción se apilan en capas en lugar de la aplicación de una sola capa de este tipo. Esto puede aparecer en dispositivos móviles -. Smartphones, tabletas

La novedad más interesante de la tecnología de 14 nanómetros puede ser SRAM: Intel llegó a un almacenamiento de 84 megabits con tamaño de celda más pequeño del mundo - 0, 050 mkm². Este 14 5 megabits por milímetro cuadrado. En comparación con 22 nm voltaje requerido caído 0, 1 a 6, 5 GHz, de 1 a 3 GHz.

Intel logra un dato muy económico: 10 Gbit / s sólo 5 requiere, 9 pJ por bit em>

10 nanómetros se requieren innovación y la transición a siete en total sólo será posible con nuevos materiales y procesos. Pero nada concreto no ha sido nombrado, aunque discutido semiconductores III-V. Esta va combinaciones de elementos del tercer grupo de la tabla periódica (aluminio, galio, indio) de los elementos del grupo del quinto (nitrógeno, fósforo, arsénico, antimonio). La movilidad de los electrones en ellos es mayor que el de silicio, que permite reducir el tamaño de los transistores. En Intel начали ven de esta manera hace unos años, tal vez dentro de unos años será el núcleo del chip de computadora en el arseniuro de galio indio.

mayor progreso se ve muy futurista: posible ultravioleta profundo, los nanotubos de carbono, los nanocables de grafeno y em>

Basado en el material Ars Technica, ExtremeTech y AnandTech.

Fuente: geektimes.ru/post/246676/

El desarrollo de métodos de caza de inteligencia artificial

Los científicos consiguieron la imagen de la luz, que se comporta como una onda y una partícula a la vez