1483

英特尔透露,计划征服10和7纳米

微处理器进一步发展可能需要的非硅

问题国际会议的半导体电路(国际固态电路研讨会)的主题今年,听起来像一个“小芯片的大数据。”本次活动从22日至2月26日在旧金山,美国加利福尼亚州。英特尔经常参加ISSCC,也不例外,2015年。尺寸为巨人英特尔和AMD是不寻常作出重要公告那里。许多报告说内部调查英特尔,它触及了潜力技术的实际应用,包括进一步降低制程技术的芯片。特别是谈到了如何攻击摩尔定律10纳米这个令人兴奋的话题。

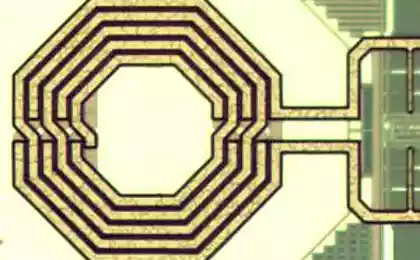

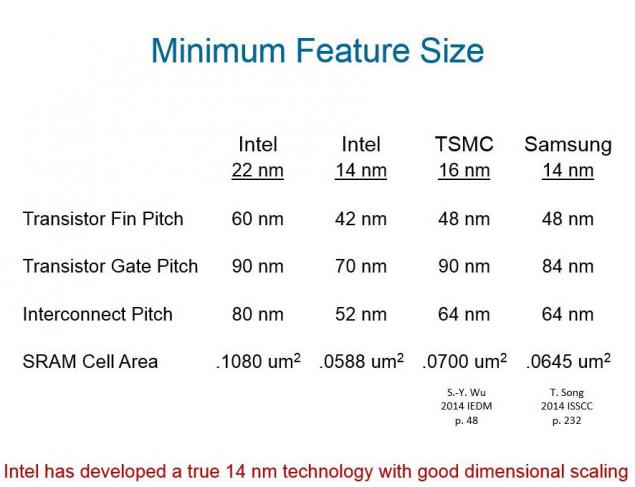

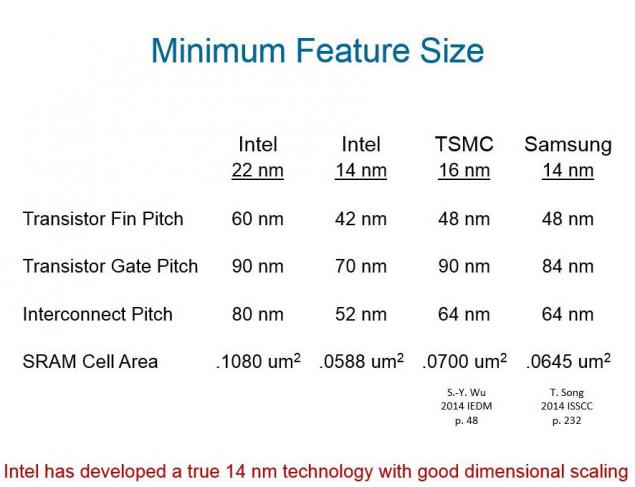

英特尔的14纳米的征服而自豪。这一成绩与困难和延误给予在6-9个月内,视类产品,但该公司仍设法实现卓越的性能,三星和台积电。英特尔认为,只有他们设法实现这一14纳米:谈论它更小的单个元素等特点,如细胞的大小SRAM

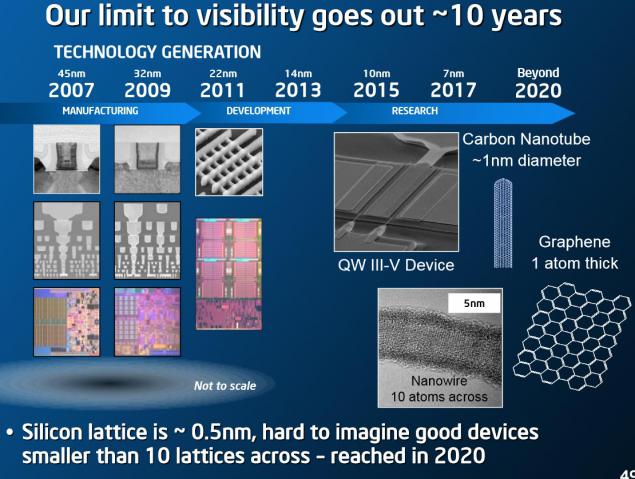

英特尔预计,过渡到10纳米将提高,但交付的具体时间并没有叫。如果你专注于此前的计划,10纳米将公布2016年年底或2017年年初。为10nm以下,进一步减少将给予非常坚硬。英特尔移动到10时

学会从他的工作在14纳米的错误,并希望能避免同样的错误

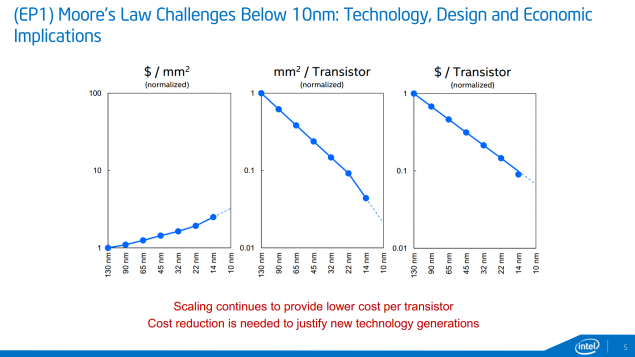

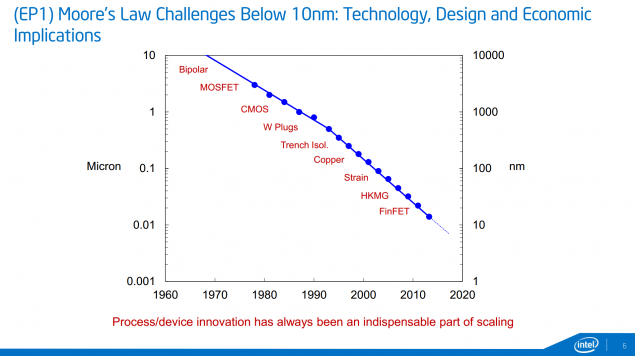

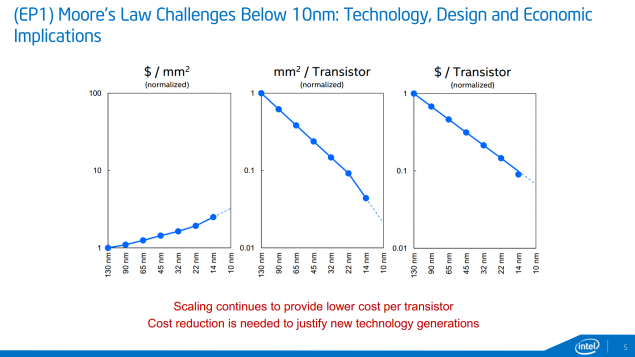

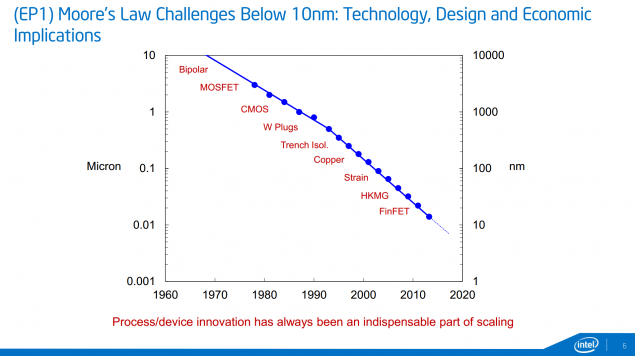

这个问题也是关于该方法的成本。在马克·玻尔的图,你可以看到各个元素如何掉价。它可以看出,14纳米显示在值稍大的下降比预期的。这是通过优化光刻工艺和使用掩模来实现。让10纳米步骤使用口罩,会更加的延误,我们已经看到,在14不会的情况。英特尔已经意识到,延误是由于测试和检验的14纳米数量增加所致。其结果是,功率校正PV试验运行10纳米半倍比为14nm的情况下更快。让固定成本将高于10纳米,但成本会使用光刻术的相同的技术落入到晶体管。英特尔认为,<一个href="https://ru.wikipedia.org/wiki/%D0%A4%D0%BE%D1%82%D0%BE%D0%BB%D0%B8%D1%82%D0%BE%D0%B3%D1%80%D0%B0%D1%84%D0%B8%D1%8F_%D0%B2_%D0%B3%D0%BB%D1%83%D0%B1%D0%BE%D0%BA%D0%BE%D0%BC_%D1%83%D0%BB%D1%8C%D1%82%D1%80%D0%B0%D1%84%D0%B8%D0%BE%D0%BB%D0%B5%D1%82%D0%B5">глубокий紫外线时,但不希望使用它,除非绝对必要的,因为它的发展缓慢的过程比预期的。

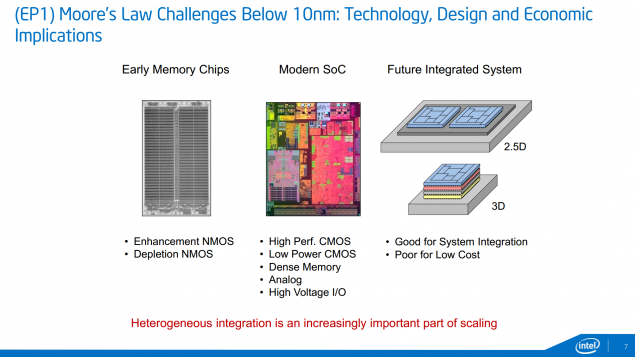

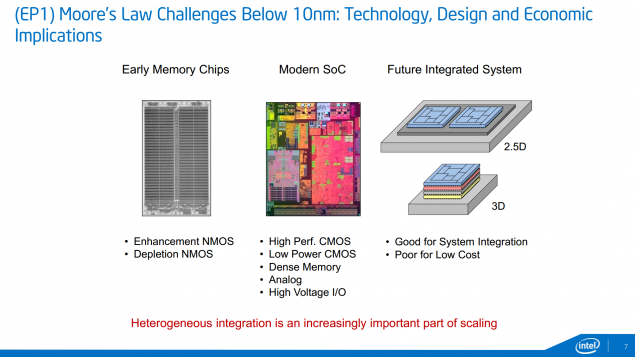

此外,研究小组谈到采用英特尔技术的3D(逐层)和2.5D(在基板上各层)。这些解决方案都不能容纳更多的晶体管:在某些情况下限制功耗(2.5D)或建立更紧凑的设计(3D)。特别是,英特尔正考虑在其中的不同的生产方法的逻辑电路的层叠代替实施这样的单层的情况。这可能会出现在移动设备 - 智能电话,平板

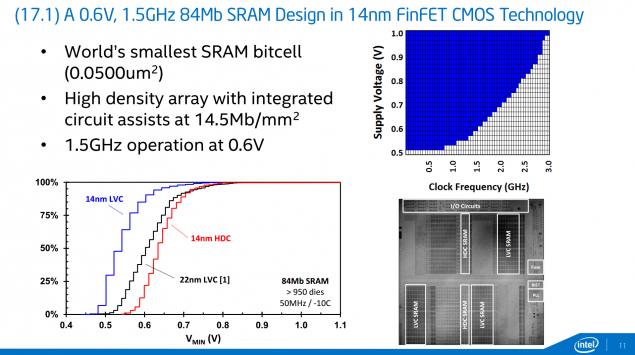

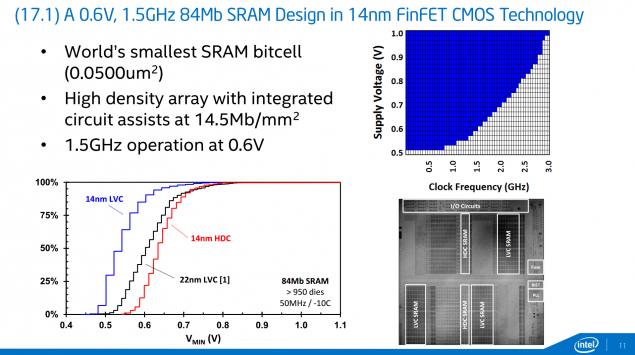

技术14纳米的最有趣的发展可以SRAM:英特尔达到了84兆的存储,有世界上最小的单元尺寸 - 0,050mkm²。这14 5每平方毫米兆。相比22nm的所需电压降到0,1至6个,5千兆赫,1至3千兆赫。

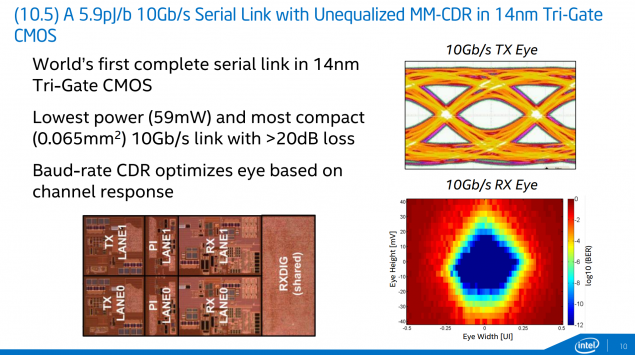

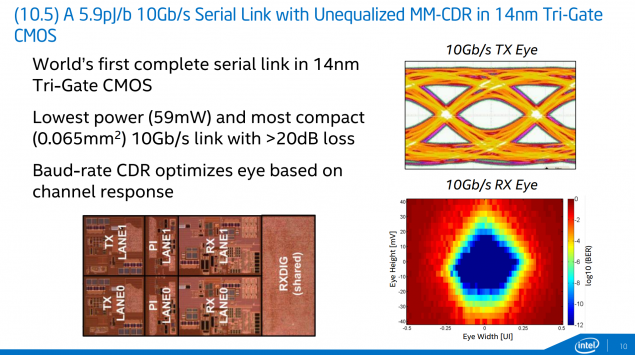

英特尔取得了非常经济数据:10 Gbit / s的只有5个要求,每比特9 PJ em>的

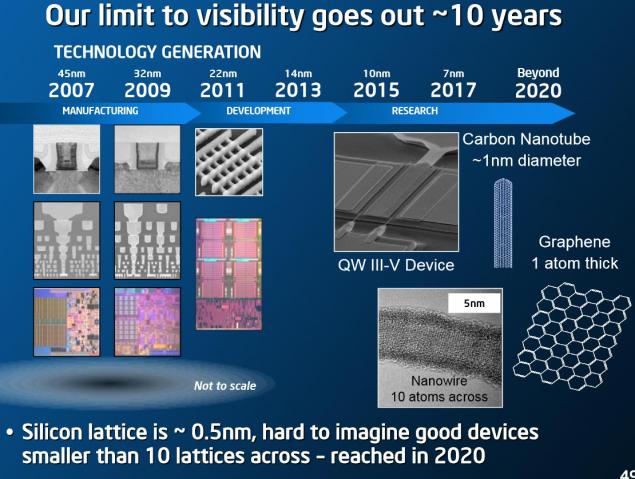

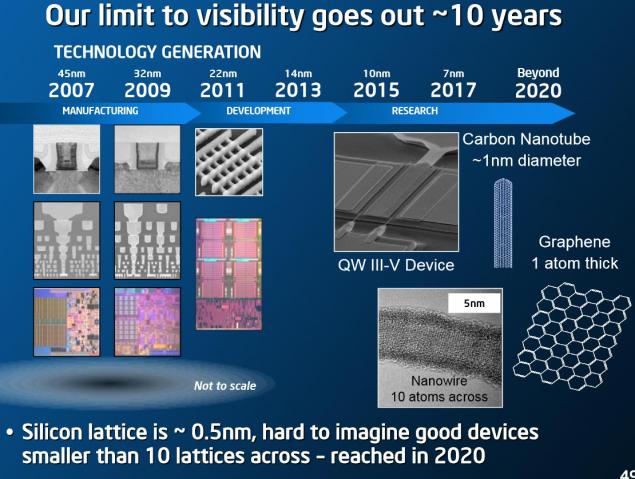

10纳米将需要创新和过渡到共7只可能用新的材料和工艺。但没有具体的还没有被命名,但讨论的III-V族半导体。此推移周期表的第三组元素组合(铝,镓,铟)从第五族元素(氮,磷,砷,锑)。在其中的电子迁移率比硅,这使得以减少晶体管的尺寸为高。英特尔<一href="http://www.extremetech.com/extreme/120353-the-future-of-cpu-scaling-exploring-options-on-the-cutting-edge">начали看起来这种方式在几年前,也许在几年将在铟镓砷化计算机芯片的核心。

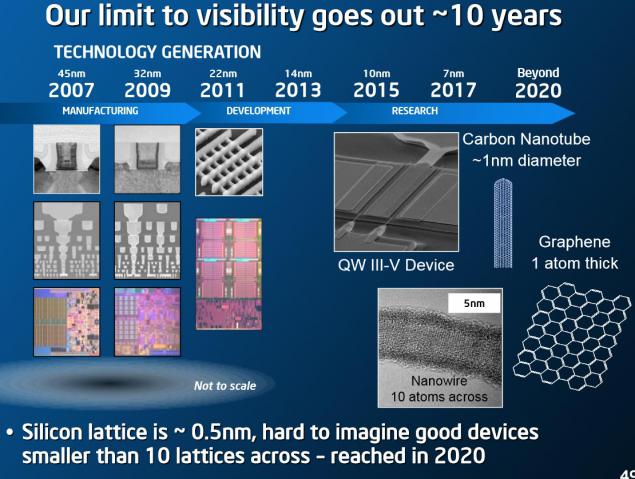

进一步的进展看上去相当前卫:可能的深紫外光,碳纳米管,石墨烯纳米线和 em>的

基于材料<一href="http://arstechnica.com/gadgets/2015/02/intel-forges-ahead-to-10nm-will-move-away-from-silicon-at-7nm/">Ars铁三角,<一个href="http://www.extremetech.com/extreme/199636-intel-at-isscc-14nm-in-the-bag-full-steam-ahead-on-10nm">ExtremeTech和<一href="http://www.anandtech.com/show/8991/intel-at-isscc-2015-reaping-the-benefits-of-14nm-and-going-beyond-10nm">AnandTech.

来源: geektimes.ru/post/246676/

问题国际会议的半导体电路(国际固态电路研讨会)的主题今年,听起来像一个“小芯片的大数据。”本次活动从22日至2月26日在旧金山,美国加利福尼亚州。英特尔经常参加ISSCC,也不例外,2015年。尺寸为巨人英特尔和AMD是不寻常作出重要公告那里。许多报告说内部调查英特尔,它触及了潜力技术的实际应用,包括进一步降低制程技术的芯片。特别是谈到了如何攻击摩尔定律10纳米这个令人兴奋的话题。

英特尔的14纳米的征服而自豪。这一成绩与困难和延误给予在6-9个月内,视类产品,但该公司仍设法实现卓越的性能,三星和台积电。英特尔认为,只有他们设法实现这一14纳米:谈论它更小的单个元素等特点,如细胞的大小SRAM

英特尔预计,过渡到10纳米将提高,但交付的具体时间并没有叫。如果你专注于此前的计划,10纳米将公布2016年年底或2017年年初。为10nm以下,进一步减少将给予非常坚硬。英特尔移动到10时

学会从他的工作在14纳米的错误,并希望能避免同样的错误

这个问题也是关于该方法的成本。在马克·玻尔的图,你可以看到各个元素如何掉价。它可以看出,14纳米显示在值稍大的下降比预期的。这是通过优化光刻工艺和使用掩模来实现。让10纳米步骤使用口罩,会更加的延误,我们已经看到,在14不会的情况。英特尔已经意识到,延误是由于测试和检验的14纳米数量增加所致。其结果是,功率校正PV试验运行10纳米半倍比为14nm的情况下更快。让固定成本将高于10纳米,但成本会使用光刻术的相同的技术落入到晶体管。英特尔认为,<一个href="https://ru.wikipedia.org/wiki/%D0%A4%D0%BE%D1%82%D0%BE%D0%BB%D0%B8%D1%82%D0%BE%D0%B3%D1%80%D0%B0%D1%84%D0%B8%D1%8F_%D0%B2_%D0%B3%D0%BB%D1%83%D0%B1%D0%BE%D0%BA%D0%BE%D0%BC_%D1%83%D0%BB%D1%8C%D1%82%D1%80%D0%B0%D1%84%D0%B8%D0%BE%D0%BB%D0%B5%D1%82%D0%B5">глубокий紫外线时,但不希望使用它,除非绝对必要的,因为它的发展缓慢的过程比预期的。

此外,研究小组谈到采用英特尔技术的3D(逐层)和2.5D(在基板上各层)。这些解决方案都不能容纳更多的晶体管:在某些情况下限制功耗(2.5D)或建立更紧凑的设计(3D)。特别是,英特尔正考虑在其中的不同的生产方法的逻辑电路的层叠代替实施这样的单层的情况。这可能会出现在移动设备 - 智能电话,平板

技术14纳米的最有趣的发展可以SRAM:英特尔达到了84兆的存储,有世界上最小的单元尺寸 - 0,050mkm²。这14 5每平方毫米兆。相比22nm的所需电压降到0,1至6个,5千兆赫,1至3千兆赫。

英特尔取得了非常经济数据:10 Gbit / s的只有5个要求,每比特9 PJ em>的

10纳米将需要创新和过渡到共7只可能用新的材料和工艺。但没有具体的还没有被命名,但讨论的III-V族半导体。此推移周期表的第三组元素组合(铝,镓,铟)从第五族元素(氮,磷,砷,锑)。在其中的电子迁移率比硅,这使得以减少晶体管的尺寸为高。英特尔<一href="http://www.extremetech.com/extreme/120353-the-future-of-cpu-scaling-exploring-options-on-the-cutting-edge">начали看起来这种方式在几年前,也许在几年将在铟镓砷化计算机芯片的核心。

进一步的进展看上去相当前卫:可能的深紫外光,碳纳米管,石墨烯纳米线和 em>的

基于材料<一href="http://arstechnica.com/gadgets/2015/02/intel-forges-ahead-to-10nm-will-move-away-from-silicon-at-7nm/">Ars铁三角,<一个href="http://www.extremetech.com/extreme/199636-intel-at-isscc-14nm-in-the-bag-full-steam-ahead-on-10nm">ExtremeTech和<一href="http://www.anandtech.com/show/8991/intel-at-isscc-2015-reaping-the-benefits-of-14nm-and-going-beyond-10nm">AnandTech.

来源: geektimes.ru/post/246676/