1546

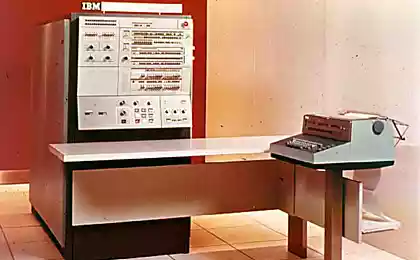

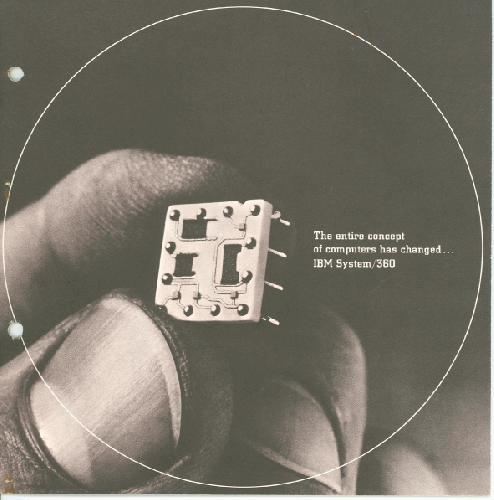

IBM System / 360 - continue to talk

In the last article, I described line IBM System / 360 "as a whole", without going too much into the details of implementation. At this time, we will continue to talk about the computer and consider its internal architecture.

Of course, no revolution System / 360 could not be accomplished if the new family of computers was not carefully thought out and designed the architecture (and later borrowed by Soviet designers). Two major leadership called «IBM System / 360 Principles of Operation» and «IBM System / 360 I / O Interface Channel to Control Unit Original Equipment Manufacturers' Information manuals».

That offers developers a System / 360? Sixteen 32-bit general-purpose registers, named R0 to R15. Four 64-bit registers for floating point numbers, they were called FP0, FP2, FP4 and FP6. One 64-bit status register (Program Status Word, or PSW), among other things contains a 24-bit address of the instruction.

Also addresses the current executable instructions, PSW save bits enables / disables the interrupt status of the program, the security key for the comparison of devices with keys and other important parameters. Privileged commands LPSW allowed to download the entire value of this register, and is used mainly for the return from the interrupt handler, restoring the state it was in before the call handler. The same set of commands allows you to manipulate individual flags in this register without causing transitions in other parts of the code.

Interrupts are divided into 5 "classes" based on priority. With each class were associated two memory double word: old and new PSW PSW. When an interrupt occurs, the current value of the PSW with the interrupt code remained in place of the old PSW, and self register loads the value of the new PSW, causing a transition to the handler. Interrupt classes were as follows (in ascending order of priority).

I / O interrupts, signaled the various events IO, including such time-consuming, such as the completion of rewinding.

Software interrupts. Signal the occurrence of one of the 15 exceptions at runtime. Some of these interrupts can be suppressed by using the appropriate reset flags in PSW.

Interrupting a call supervisor. Occurred as a result of instructions addressed to the supervisor.

External interrupts. Occurs as a result of external events, such as timer interrupt or pressing.

Interruption of machine check occurs when a hardware failure, such as a parity error when checking the contents of the registers.

As has been clear for memory addressing used 24 bits that can address 16 MB of memory, but since the model 67 the opportunity to 32-bit addressing, which expanded the scope of addressable (theoretically) up to 4 gigabytes of memory. We used a big-endian order, ie from older to younger. Different instruction allows to work with bytes, half-words (2 bytes), full words (4 bytes), dual and quad words (respectively 8 and 16 bytes).

Nominally supports the following data types:

Integers or half the length of the whole word

Two species packed into a binary format decimal

Fractional floating-point numbers (the nuances of implementation depended on the version)

Characters are stored in one byte each

Addressing often use the "truncated": instructions do not contain the full address, but only the offset from the base address contained in one of the general purpose registers.

Instructions may be a 2, 4 or 6 bytes, while the operation code is stored in the zeroth byte, and the rest is the description of the operands. Instruction is aligned to halfword boundaries, so the least significant bit of the address of the current instruction has always been zero.

Interestingly in the System / 360 was implemented IO. Input-output operations performed conceptually distinct processors, called "channels". A channel had its own set of instructions, and they worked with memory, regardless of the program executed by the CPU. In the low-cost models to support the channels used "engine" of the CPU microcode, the more expensive - channels were placed in their own closets.

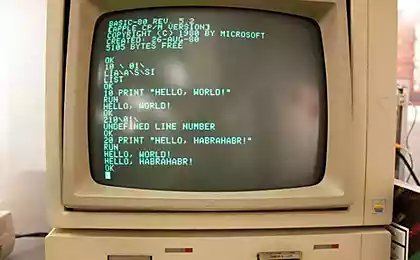

Very unusual for IBM approached the management of their computers. They identified a specific set of functions, without specifying which ones using physical means, they should be implemented. This allowed us to control the universal, not dependent on a particular iron, for return instructions and output the results in the course could go any hardware buttons, dials, keyboard, text and graphics on the monitors, etc. Any reference to a "button" or "switch" could mean any of the possible inputs, starting with the light pen and ending choice options on the screen using the keyboard input.

In various models of the System / 360 used different additional features, extend the base.

Account Security. If the system supports this option, each block external storage size of 2 kb was assigned a key that is checked when writing to this storage channel. That is, each channel can only write in "their" blocks. Usually the channel with zero location used by the operating system, and check the key for him was not carried out. This approach lets you protect system files from user programs erasure. In very rare models just had the opportunity to exhibit and read protection.

Support multisystem. Extended instruction set allows you to work multiple processors simultaneously.

Direct control. This option provides support for 6 external signal lines, which could be used for the needs of the user.

Interval timer. With this option, the processor carries out periodic decrement the words stored in the memory at the address 0x50, when this value reaches zero, the interrupt occurs. Younger models reduced the number with the frequency coincides with the frequency of the mains (50 or 60 Hz), the older models were equipped with timers where higher resolution.

In general, about the System / 360, you can talk a lot, so if there is interest, I will continue the theme of the next article.

Source: habrahabr.ru/post/221587/